- ╩’║ŻĮ╠ė²╝»łFšōē» (http://www.brpp.cn/bbs/index.asp)

-- FPGA│§ųą╝ē (http://www.brpp.cn/bbs/list.asp?boardid=25)

---- ĮĄĄ═FPGA╣”║─Ą─įO(sh©©)ėŗ╝╝Ū╔ (http://www.brpp.cn/bbs/dispbbs.asp?boardid=25&id=2764)

-- ░l(f©Ī)▓╝ĢrķgŻ║2010-12-19 10:09:41

-- ĮĄĄ═FPGA╣”║─Ą─įO(sh©©)ėŗ╝╝Ū╔

╩╣ė├▀@ą®įO(sh©©)ėŗ╝╝Ū╔║═ISE╣”─▄Ęų╬÷╣żŠ▀üĒ┐žųŲ╣”║─

ĪĪĪĪ ą┬ę╗┤· FPGAĄ─╦┘Č╚ūāĄ├įĮüĒįĮ┐ņ,├▄Č╚ūāĄ├įĮüĒįĮĖ▀,▀ē▌ŗ┘Yį┤ę▓įĮüĒįĮČÓĪŻ─Ū├┤╚ń║╬▓┼─▄┤_▒Ż╣”║─▓╗ļS▀@ą®ę╗Ųį÷╝ė─žŻ┐║▄ČÓįO(sh©©)ėŗŠ±ō±┐╔ęįė░ĒæŽĄĮy(t©»ng)Ą─╣”║─,▀@ą®Š±ō±░³└©Å─’@ęŖĄ─Ų„╝■▀xō±ĄĮ╝ÜąĪĄ─╗∙ė┌╩╣ė├Ņl┬╩Ą─ĀŅæB(t©żi)ÖCųĄĄ─▀xō±Ą╚ĪŻ

ĪĪĪĪ ×ķ┴╦Ė³║├Ąž└ĒĮŌ▒Š╬─īóę¬ėæšōĄ─įO(sh©©)ėŗ╝╝Ū╔×ķ╩▓├┤─▄ē“╣Ø(ji©”)╩Ī╣”║─,╬ęéāŽ╚ī”╣”║─ū÷ę╗éĆ║åå╬ĮķĮBĪŻ

ĪĪĪĪ ╣”║─░³║¼ā╔éĆę“╦žŻ║äėæB(t©żi)╣”║─║═ņoæB(t©żi)╣”║─ĪŻäėæB(t©żi)╣”║─╩ŪųĖī”Ų„╝■ā╚(n©©i)Ą─╚▌ąįžō▌d│õĘ┼ļŖ╦∙ąĶĄ─╣”║─ĪŻ╦³║▄┤¾│╠Č╚╔Ž╚ĪøQė┌Ņl┬╩ĪóļŖē║║═žō▌dĪŻ▀@╚²éĆūā┴┐ųąĄ─├┐éĆūā┴┐Š∙į┌─·Ą──│ĘN┐žųŲų«Ž┬ĪŻ

ĪĪĪĪ äėæB(t©żi)╣”║─ = ļŖ╚▌Ī┴ļŖē║2Ī┴Ņl┬╩

ĪĪĪĪ ņoæB(t©żi)╣”║─╩ŪųĖė╔Ų„╝■ųą╦∙ėąŠ¦¾w╣▄Ą─ą╣┬®ļŖ┴„Ż©į┤śOĄĮ┬®śOęį╝░¢┼śOą╣┬®,│Ż│Ż╝»ųą×ķņoų╣ļŖ┴„Ż®ę²ŲĄ─╣”║─,ęį╝░╚╬║╬Ųõ╦¹║ŃČ©╣”║─ąĶŪ¾ų«║═ĪŻą╣┬®ļŖ┴„║▄┤¾│╠Č╚╔Ž╚ĪøQė┌ĮY(ji©”)£ž║═Š¦¾w╣▄│▀┤ńĪŻ

ĪĪĪĪ ║ŃČ©╣”║─ąĶŪ¾░³└©ę“ĮKĮėŻ©╚ń╔Ž└ŁļŖūĶŻ®Č°įņ│╔Ą─ļŖ┴„ą╣┬®ĪŻø]ėąČÓ╔┘┤ļ╩®┐╔ęį▓╔ė├üĒė░Ēæą╣┬®,Ą½║ŃČ©╣”║─┐╔ęįĄ├ĄĮ┐žųŲĪŻ

▒Mįń┐╝æ]╣”║─

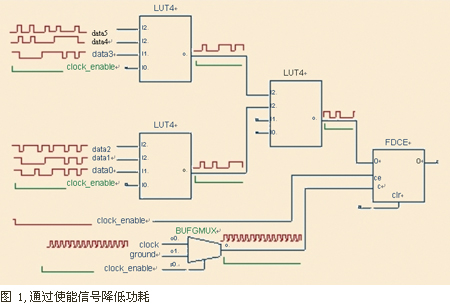

ĪĪĪĪ ─·į┌įO(sh©©)ėŗĄ─įńŲ┌ļAČ╬ū÷│÷Ą─╣”║─øQČ©ė░ĒæūŅ┤¾ĪŻøQČ©▓╔ė├╩▓├┤į¬╝■ī”╣”║─Š▀ėąųž┤¾ęŌ┴x,Č°į┌ĢrńŖ╔Ž▓Õ╚ļę╗éĆ BUFGMUX ätė░Ēæ╔§╬óĪŻī”╣”║─Ą─┐╝æ]įĮįńįĮ║├ĪŻ

ŪĪ«ö(d©Īng)?sh©┤)─į¬╝?

ĪĪĪĪ ▓ó▓╗╩Ū╦∙ėąį¬╝■Č╝Š▀ėąŽÓ═¼Ą─ņoų╣╣”║─ĪŻĖ∙ō■(j©┤)Ųš▒ķęÄ(gu©®)ät,Ų„╝■╣ż╦ć╝╝ąg(sh©┤)│▀┤ńįĮąĪ,ą╣┬®╣”║─įĮ┤¾ĪŻĄ½▓ó▓╗╩Ū╦∙ėą╣ż╦ć╝╝ąg(sh©┤)Č╝ę╗śėĪŻ└²╚ń,ī”ė┌ 90 nm ╝╝ąg(sh©┤)üĒšf,Virtex-4 Ų„╝■┼cŲõ╦¹ 90 nm FPGA ╝╝ąg(sh©┤)ų«ķgį┌ņoų╣╣”║─ĘĮ├µ┤µį┌’@ų°▓Ņ«É,

ĪĪĪĪ ╚╗Č°,į┌ņoų╣╣”║─ļS╣ż╦ć╝╝ąg(sh©┤)┐sąĪČ°į÷╝ėĄ─═¼Ģr,äėæB(t©żi)╣”║─ģsļSų«£pąĪ,▀@╩Ūė╔ė┌▌^ąĪĄ─╣ż╦ćėąų°Ė³Ą═Ą─ļŖē║║═ļŖ╚▌ĪŻ┐╝æ]║├──ĘN╣”║─ī”─ŃĄ─įO(sh©©)ėŗė░ĒæĖ³┤¾Ī¬Ī¬┤²ÖCŻ©ņoų╣Ż®╣”║─▀Ć╩ŪäėæB(t©żi)╣”║─ĪŻ

ĪĪĪĪ │²═©ė├ŪąŲ¼▀ē▌ŗå╬į¬═Ō,╦∙ėąXilinxŲ„╝■Č╝Š▀ėąīŻķT▀ē▌ŗĪŻŲõą╬╩ĮėąēK RAMĪó18Ī┴18 │╦Ę©Ų„ĪóDSP48 ēKĪóSRL16s,ęį╝░Ųõ╦¹▀ē▌ŗĪŻ▀@▓╗āHį┌ė┌īŻķT▀ē▌ŗŠ▀ėąĖ³Ė▀Ą─ąį─▄,▀Ćį┌ė┌╦³éāŠ▀ėąĖ³Ą═Ą─├▄Č╚,ę“Č°ī”ė┌ŽÓ═¼Ą─▓┘ū„┐╔ęįŽ¹║─▌^╔┘Ą─╣”┬╩ĪŻįu╣└─·Ą─Ų„╝■▀xĒŚĢr,šł┐╝æ]īŻķT▀ē▌ŗĄ─ŅÉą═║═öĄ(sh©┤)┴┐ĪŻ

ĪĪĪĪ ▀xō±▀m«ö(d©Īng)?sh©┤)?I/O ś╦(bi©Īo)£╩(zh©│n)ę▓┐╔ęį╣Ø(ji©”)╩Ī╣”║─ĪŻ▀@ą®Č╝╩Ū║åå╬Ą─øQČ©,╚ń▀xō±ūŅĄ═Ą─“ī(q©▒)äėÅŖČ╚╗“▌^Ą═Ą─ļŖē║ś╦(bi©Īo)£╩(zh©│n)ĪŻ«ö(d©Īng)ŽĄĮy(t©»ng)╦┘Č╚ę¬Ū¾╩╣ė├Ė▀╣”┬╩ I/O ś╦(bi©Īo)£╩(zh©│n)Ģr,ėŗäØę╗éĆ╚▒╩ĪĀŅæB(t©żi)ęįĮĄĄ═╣”║─ĪŻėąĄ─ I/O ś╦(bi©Īo)£╩(zh©│n)Ż©╚ń GTL/+Ż®ąĶę¬╩╣ė├ę╗éĆ╔Ž└ŁļŖūĶ▓┼─▄š²│Ż╣żū„ĪŻę“┤╦╚ń╣¹įō I/O Ą─╚▒╩ĪĀŅæB(t©żi)×ķĖ▀ļŖŲĮČ°▓╗╩ŪĄ═ļŖŲĮ,Š═┐╔ęį╣Ø(ji©”)╩Ī═©▀^įōĮKĮėļŖūĶĄ─ų▒┴„╣”║─ĪŻī”ė┌ GTL+,īó50”ĖĮKĮėļŖūĶĄ─▀m«ö(d©Īng)╚▒╩ĪĀŅæB(t©żi)įO(sh©©)ų├×ķ 1.5V,┐╔╩╣├┐éĆ I/O ╣Ø(ji©”)╩Ī╣”║─ 30 mAĪŻ

öĄ(sh©┤)ō■(j©┤)╩╣─▄

ĪĪĪĪ «ö(d©Īng)┐éŠĆ╔ŽĄ─öĄ(sh©┤)ō■(j©┤)┼c╝─┤µŲ„ŽÓĻP(gu©Īn)Ģr,Įø(j©®ng)│Ż╩╣ė├Ų¼▀x╗“ĢrńŖ╩╣─▄▀ē▌ŗüĒ┐žųŲ╝─┤µŲ„Ą─╩╣─▄ĪŻ▀Mę╗▓ĮüĒšf,▒Mįńī”įō▀ē▌ŗ▀MąąĪ░öĄ(sh©┤)ō■(j©┤)╩╣─▄Ī▒,ęįūĶų╣öĄ(sh©┤)ō■(j©┤)┐éŠĆ┼cĢrńŖ╩╣─▄╝─┤µŲ„ĮM║Ž▀ē▌ŗų«ķg▓╗▒žę¬Ą─▐D(zhu©Żn)ōQ,╚ńłD 1 ╦∙╩ŠĪŻ╝t╔½▓©ą╬▒Ē╩ŠįŁįO(sh©©)ėŗ;ŠG╔½▓©ą╬▒Ē╩Šą▐Ė─║¾Ą─įO(sh©©)ėŗĪŻ

ĪĪĪĪ ┴Ēę╗ĘN▀xō±╩Ūį┌ļŖ┬Ę░Õ╔ŽČ°▓╗╩Ūį┌ąŠŲ¼╔Ž▀Mąą▀@ĘNĪ░öĄ(sh©┤)ō■(j©┤)╩╣─▄Ī▒ĪŻęį▒M┐╔─▄£pąĪ╠Ä└ĒŲ„ĢrńŖų▄Ų┌ĪŻ┤╦Ė┼─Ņ╩Ū╩╣ė├ CPLD Å─╠Ä└ĒŲ„ąČ▌d║åå╬╚╬äš(w©┤),ęį▒Ń╩╣ŲõĖ³ķLĢrķgĄž╠Äė┌┤²ÖC─Ż╩ĮĪŻ

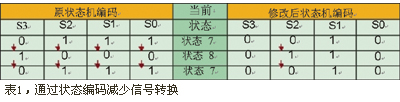

ĪĪĪĪ ūī╬ęéāüĒ┐┤ę╗éĆį┌ĀŅæB(t©żi) 7 ║═ĀŅæB(t©żi) 8 ų«ķgŅlĘ▒▀MąąĀŅæB(t©żi)▐D(zhu©Żn)ōQĄ─ĀŅæB(t©żi)ÖCĪŻ╚ń╣¹─·×ķįōĀŅæB(t©żi)ÖC▀xō±Č■▀MųŲŠÄ┤a,īóęŌ╬Čų°ī”ė┌├┐┤╬ĀŅæB(t©żi) 7 ║═ĀŅæB(t©żi) 8 ų«ķgĄ─ĀŅæB(t©żi)▐D(zhu©Żn)ōQ,īóėą╦─╬╗ąĶę¬Ė─ūāĀŅæB(t©żi),╚ń▒Ē 1 ╦∙╩ŠĪŻ╚ń╣¹ĀŅæB(t©żi)ÖC▓╔ė├Ė±└ū┤aČ°▓╗╩ŪČ■▀MųŲ┤aüĒįO(sh©©)ėŗ,ät▀@ā╔éĆĀŅæB(t©żi)ų«ķgĄ─▐D(zhu©Żn)ęŲ╦∙ąĶĄ─▀ē▌ŗ▐D(zhu©Żn)ōQĄ─öĄ(sh©┤)┴┐īóĮĄų┴āHę╗╬╗ĪŻ┴Ē═Ō,╚ń╣¹īóĀŅæB(t©żi) 7 ║═ 8 ĘųäeŠÄ┤a×ķ 0010 ║═ 0011,ę▓┐╔ęį▀_ĄĮ═¼śėĄ─ą¦╣¹ĪŻ

ĢrńŖ╣▄└Ē

ĪĪĪĪ į┌ę╗éĆįO(sh©©)ėŗĄ─╦∙ėą╬³╩š╣”║─Ą─ą┼╠¢«ö(d©Īng)ųą,ĢrńŖ╩Ūū’┐²Ą£?zh©│n)ūĪŻļm╚╗ę╗éĆĢrńŖ┐╔─▄▀\ąąį┌ 100 MHz,Ą½Å─įōĢrńŖ┼╔╔·│÷Ą─ą┼╠¢ģs═©│Ż▀\ąąį┌ų„ĢrńŖŅl┬╩Ą─▌^ąĪĘų┴┐Ż©═©│Ż×ķ 12% ~ 15%Ż®ĪŻ┤╦═Ō,ĢrńŖĄ─╔╚│÷ę╗░Ńę▓▒╚▌^Ė▀Ī¬Ī¬▀@ā╔éĆę“╦ž’@╩Š,×ķ┴╦ĮĄĄ═╣”║─,æ¬(y©®ng)«ö(d©Īng)šJšµčąŠ┐ĢrńŖĪŻ

ĪĪĪĪ ╚ń╣¹įO(sh©©)ėŗĄ──│éĆ▓┐Ęų┐╔ęį╠Äė┌ĘŪ╗ŅäėĀŅæB(t©żi),ät┐╔ęį┐╝æ]╩╣ė├ę╗éĆ BUFG-MUX üĒĮ¹ų╣ĢrńŖśõĘŁ▐D(zhu©Żn),Č°▓╗╩Ū╩╣ė├ĢrńŖ╩╣─▄ĪŻĢrńŖ╩╣─▄īóūĶų╣╝─┤µŲ„▀Mąą▓╗▒žę¬Ą─ĘŁ▐D(zhu©Żn),Ą½ĢrńŖśõ╚į╚╗Ģ■ĘŁ▐D(zhu©Żn),Ž¹║─╣”┬╩ĪŻ▓╗▀^▓╔ė├ĢrńŖ╩╣─▄┐é▒╚╩▓├┤┤ļ╩®ę▓ø]ėąÅŖĪŻ

ĪĪĪĪ Ė¶ļxĢrńŖęį╩╣ė├ūŅ╔┘öĄ(sh©┤)┴┐Ą─ą┼╠¢ģ^(q©▒)ĪŻ▓╗╩╣ė├Ą─ĢrńŖśõą┼╠¢ģ^(q©▒)▓╗Ģ■ĘŁ▐D(zhu©Żn),Å─Č°ĮĄĄ═įōĢrńŖŠW(w©Żng)Įj(lu©░)Ą─žō▌dĪŻūą╝Ü▓╝Šų┐╔ęįį┌▓╗ė░ĒæīŹļHįO(sh©©)ėŗĄ─ŪķørŽ┬▀_ĄĮ┤╦─┐ś╦(bi©Īo)ĪŻ

ĪĪĪĪ ī” FPGA ’@╚╗ę▓┐╔ęį╩╣ė├═¼ę╗Ė┼─ŅĪŻļm╚╗ FPGA ▓╗ę╗Č©ōĒėą┤²ÖC─Ż╩Į,Ą½╩╣ė├ę╗éĆ CPLD ųą═ŠÖ┌Įž┐éŠĆöĄ(sh©┤)ō■(j©┤)▓óėą▀xō±ĄžīóöĄ(sh©┤)ō■(j©┤)ü╦═ĄĮ FPGA ę▓┐╔ęį╩Ī╚ź▓╗▒žę¬Ą─▌ö╚ļ▐D(zhu©Żn)ōQĪŻ

ĪĪĪĪ CoolRunner-II CPLD ░³║¼ę╗ĘNĘQ×ķĪ░öĄ(sh©┤)ō■(j©┤)ķT┐žĪ▒Ą─╣”─▄,┐╔ęįĮ¹ų╣ę²─_╔ŽĄ─▀ē▌ŗ▐D(zhu©Żn)ōQĄĮ▀_ CPLD Ą─ā╚(n©©i)▓┐▀ē▌ŗĪŻįōöĄ(sh©┤)ō■(j©┤)ķT┐ž╩╣─▄┐╔═©▀^Ų¼╔Ž▀ē▌ŗ╗“ę²─_üĒ┐žųŲĪŻ

ĀŅæB(t©żi)ÖCįO(sh©©)ėŗ

ĪĪĪĪ Ė∙ō■(j©┤)ŅA(y©┤)£yĄ─Ž┬ę╗ĀŅæB(t©żi)Śl╝■┴ą┼eĀŅæB(t©żi)ÖC,▓ó▀xō±│ŻæB(t©żi)ų«ķg▐D(zhu©Żn)ōQ╬╗▌^╔┘Ą─ĀŅæB(t©żi)ųĄĪŻ▀@śė,─·Š═─▄ē“▒M┐╔─▄£p╔┘ĀŅæB(t©żi)ÖCŠW(w©Żng)Įj(lu©░)Ą─▐D(zhu©Żn)ōQ┴┐Ż©Ņl┬╩Ż®ĪŻ┤_Č©│ŻæB(t©żi)▐D(zhu©Żn)ōQ║═▀xō±▀m«ö(d©Īng)?sh©┤)─ĀŅæB(t©żi)ųĄ,╩ŪĮĄĄ═╣”║─Ūęī”įO(sh©©)ėŗė░Ēæ▌^ąĪĄ─ę╗ĘN║åå╬ĘĮĘ©ĪŻŠÄ┤aą╬╩ĮįĮ║åå╬Ż©ę╗╬╗ėąą¦ŠÄ┤a╗“Ė±└ū┤aŻ®,╩╣ė├Ą─ĮŌ┤a▀ē▌ŗę▓Ģ■įĮ╔┘ĪŻ

ĪĪ╣”║─╣└╦Ń╣żŠ▀

ĪĪĪĪ ┘Éņ`╦╝╠ß╣®┴╦ā╔ĘNą╬╩ĮĄ─╣”║─╣└╦Ń╣żŠ▀Ż║ę╗ĘNĮąū÷ Web Power Tools Ą─įO(sh©©)ėŗŪ░╣żŠ▀║═ę╗ĘNĮąū÷ Xpower Ą─įO(sh©©)ėŗ║¾╣żŠ▀ĪŻWeb Power Tools ┐╔═©▀^ www.xilinx.com/cn/power ½@Ą├,╦³╠ß╣®┴╦Ė∙ō■(j©┤)▀ē▌ŗ└¹ė├┬╩┤¾Ė┼╣└ėŗū÷│÷Ą─╣”║─╣└╦ŃĪŻ└¹ė├╦³,─·┐╔ęįāHæ{įO(sh©©)ėŗ└¹ė├┬╩╣└ėŗŠ═─▄½@Ą├╣”║─įu╣└,Č°¤oąĶīŹļHįO(sh©©)ėŗ╬─╝■ĪŻ

ĪĪĪĪ XPower ╩Ūę╗ĘNįO(sh©©)ėŗ║¾╣żŠ▀,ė├ė┌Ęų╬÷īŹļHŲ„╝■└¹ė├┬╩,▓óĮY(ji©”)║ŽīŹļHĄ─▀m┼õ║¾ (post-fit) Ę┬šµöĄ(sh©┤)ō■(j©┤)Ż©VCD ╬─╝■Ė±╩ĮŻ®,Įo│÷īŹļH╣”║─öĄ(sh©┤)ō■(j©┤)ĪŻ└¹ė├ Xpower,─·┐╔ęįį┌═Ļ╚½▓╗Įėė|ąŠŲ¼Ą─ŪķørŽ┬Ęų╬÷įO(sh©©)ėŗĖ─ūāī”┐é╣”║─Ą─ė░ĒæĪŻ

╗∙ė┌ Web Ą─╣”║─╣żŠ▀

ĪĪĪĪ ╗∙ė┌ Web Ą─╣”║─╣└ėŗ╩Ūį┌įO(sh©©)ėŗ┴„│╠Ą─įńŲ┌½@Ą├Ų„╝■╣”║─ŪķørĄ─ūŅ┐ņĮ▌║═ūŅĘĮ▒ŃĄ─ĘĮĘ©ĪŻ▀@ą®╣żŠ▀├┐éĆ╝ŠČ╚Č╝Ģ■░l(f©Ī)▓╝ą┬░µ▒Š,ę“┤╦ą┼Žó┐é╩ŪūŅą┬Ą─,Ūę▓╗ąĶę¬░▓čb╗“Ž┬▌d,ų╗ąĶę¬ōĒėą╗ź┬ō(li©ón)ŠW(w©Żng)▀BĮė║═ Web ×gė[Ų„╝┤┐╔ĪŻ─·┐╔ęįųĖČ©įO(sh©©)ėŗģóöĄ(sh©┤)▓ó▒Ż┤µ║═╝ė▌dįO(sh©©)ėŗįO(sh©©)ų├,├Ō╚ź┴╦═©▀^Į╗╗ź╩╣ė├ųžą┬▌ö╚ļįO(sh©©)ėŗģóöĄ(sh©┤)Ą─┬ķ¤®ĪŻų╗ę¬ėąī”įO(sh©©)ėŗąą×ķĄ─╣└ėŗ▓ó▀xČ©─┐ś╦(bi©Īo)Ų„╝■╝┤┐╔ķ_╩╝ĪŻ

XpowerŻ║╝»│╔Ą─įO(sh©©)ėŗīŻė├╣”║─Ęų╬÷

ĪĪĪĪ Xpower ╩Ū╦∙ėą Xilinx ISEįO(sh©©)ėŗ╣żŠ▀Ą─ę╗éĆ├Ō┘MĮM╝■,─·┐╔ęį└¹ė├╦³ī”─·Ą─╗∙ė┌įO(sh©©)ėŗĄ─╣”║─ąĶŪ¾▀Mąąįö╝ÜĄ├ČÓĄ─╣└ėŗĪŻXPower ╩Ūį┌ė│╔õ╗“▓╝Šų║═▓╝ŠĆ║¾įO(sh©©)ėŗĄ─╗∙ĄA(ch©│)╔Žī”Ų„╝■╣”║─▀Mąą╣└ėŗĄ─ĪŻ

ĪĪĪĪ ī”ė┌│╔╩ņĄ─═Č«a(ch©Żn)Ą─ FPGA ║═ CPLD,XPower ėŗ╦Ń│÷Ą─╣”║─╣└ėŗĄ─ŲĮŠ∙įO(sh©©)ėŗ┼·┴┐š`▓Ņ (suite error) ąĪė┌ 10%ĪŻ╦³īó░čŲ„╝■öĄ(sh©┤)ō■(j©┤)┼c─·Ą─įO(sh©©)ėŗ╬─╝■ĮY(ji©”)║ŽŲüĒŠC║Ž┐╝æ],▓ó░┤šš─·Ą─īŻķTįO(sh©©)ėŗą┼ŽóĮo│÷╣└ėŗŲ„╝■╣”║─Ą─Ė▀Š½Č╚ł¾ĖµĪŻ

ĪĪĪĪ XPowerų▒Įė╝»│╔į┌ ISE ▄ø╝■ųą,┐╔╠ß╣®īė┤╬╗»Ą─įö╝ÜĄ─╣”║─’@╩ŠĪóįö╝ÜĄ─┐éĮY(ji©”)ł¾Ėµ║═╣”║─Ž“?q©▒)?╝┤╩╣╩Ūą┬ė├æ¶ę▓┐╔▌pęū╔Ž╩ųĪŻXPower ┐╔Įė╩▄Ę┬šµĄ─įO(sh©©)ėŗ╗ŅäėöĄ(sh©┤)ō■(j©┤),▓ó┐╔ęį GUI ─Ż╩Į║═┼·╠Ä└Ē─Ż╩Į▀\ąąĪŻ

ĪĪĪĪ XPower īó┐╝æ]įO(sh©©)ėŗųąĄ─├┐éĆŠW(w©Żng)Įj(lu©░)║═▀ē▌ŗį¬╦žĪŻISE įO(sh©©)ėŗ╬─╝■╠ß╣®£╩(zh©│n)┤_Ą─┘Yį┤╩╣ė├Ūķør;XPower Į╗▓µģó┐╝▓╝ŠĆą┼Žóęį╝░╠žąį╗»ļŖ╚▌öĄ(sh©┤)ō■(j©┤)ĪŻė┌╩Ū╬’└Ē┘Yį┤ßśī”ļŖ╚▌▀Mąą╠žąį╗»ĪŻįO(sh©©)ėŗ╠žąį╗»īóī”ą┬Ų„╝■│ų└m(x©┤)▀Mąą,ęįĮo│÷ūŅŠ½┤_Ą─ĮY(ji©”)╣¹ĪŻXpower ╩╣ė├┴╦ŠW(w©Żng)Įj(lu©░)ĘŁ▐D(zhu©Żn)╦┘┬╩║═▌ö│÷žō▌dĪŻ╚╗║¾ XPower ėŗ╦Ń╣”║─║═ĮY(ji©”)£ž,▀Ć┐╔ęį’@╩Šå╬éĆŠW(w©Żng)Įj(lu©░)Ą─╣”║─öĄ(sh©┤)ō■(j©┤)ĪŻ

ĮY(ji©”)šō

ĪĪĪĪ ī”Ė³▒Ńę╦║═Ė³║åå╬Ą─¤ß╣▄└Ēęį╝░┼cŪ░čž FPGA ▓╗öÓ╠ßĖ▀Ą─╣”║─ąĶŪ¾ŽÓŲź┼õĄ─ļŖį┤Ą─▓╗öÓį÷ķLĄ─ąĶŪ¾,īóĄ═╣”║─įO(sh©©)ėŗĄ─Ė┼─Ņ╠ß╔²ĄĮę╗éĆ╚½ą┬Ą─Ė▀Č╚ĪŻ┘Éņ`╦╝ūŅą┬Ų„╝■ Virtex-4 FPGA ╠ß╣®┴╦ 90 nm ╣ż╦ć╝╝ąg(sh©┤)Ą─Ė▀ąį─▄,ģs▒▄├Ō┴╦ŅA(y©┤)ŽļųąņoæB(t©żi)╣”║─Ą─’@ų°į÷┤¾ĪŻ╩╣ė├┘Éņ`╦╝╣”║─╣└╦Ń╣żŠ▀▓óū±čŁĄ═╣”║─įO(sh©©)ėŗ┐╝æ]╩┬ĒŚ,ØMūŃ─·Ą─╣”║──┐ś╦(bi©Īo)īó▒╚ęį═∙╚╬║╬Ģr║“Č╝Ė³╝ė╚▌ęūĪŻ